## 2M-BIT [256K x 8] CMOS FLASH MEMORY

## FEATURES

- 262,144x 8 only

- Fast access time: 70/90/120ns

- Low power consumption

30mA maximum active current

- 1µA typical standby current

- Programming and erasing voltage 5V ± 10%

- Command register architecture

- Byte Programming (7us typical)

- Block Erase (16K-Byte x1, 8K-Byte x 2, 32K-Byte x1, and 64K-Byte x 3)

- Auto Erase (chip & block) and Auto Program

Automatically erase any combination of sectors or the whole chip with Erase Suspend capability.

Automatically programs and verifies data at specified

- address

- Erase Suspend/Erase Resume

Suspends an erase operation to read data from, or program data to, a sector that is not being erased, then resumes the erase operation.

Status Reply

- Data polling & Toggle bit for detection of program and erase cycle completion.

Sector protection

- Hardware method to disable any combination of sectors from program or erase operations

- Sector protect/unprotect for 5V only system or 5V/ 12V system

- 100,000 minimum erase/program cycles

- Latch-up protected to 100mA from -1 to VCC+1V

- Boot Code Sector Architecture

T = Top Boot Sector

- B = Bottom Boot Sector

- Hardware RESET pin

- Resets internal state machine to read mode

- Low VCC write inhibit is equal to or less than 3.2V

- Package type:

- 32-pin PDIP

- 32-pin PLCC

- 32-pin TSOP (Type 1)

## **GENERAL DESCRIPTION**

The MX29F002T/B is a 2-mega bit Flash memory organized as 256K bytes of 8 bits only. MXIC's Flash memories offer the most cost-effective and reliable read/write nonvolatile random access memory. The MX29F002T/B is packaged in 32-pin PDIP,PLCC and 32-pin TSOP(I). It is designed to be reprogrammed and erased in-system or instandard EPROM programmers.

The standard MX29F002T/B offers access time as fast as 70ns, allowing operation of high-speed microprocessors without wait states. To eliminate bus contention, the MX29F002T/B has separate chip enable ( $\overline{\text{CE}}$ ) and output enable ( $\overline{\text{OE}}$ ) controls.

MXIC's Flash memories augment EPROM functionality with in-circuit electrical erasure and programming. The MX29F002T/B uses a command register to manage this functionality. The command register allows for 100% TTL level control inputs and fixed power supply levels during erase and programming, while maintaining maximum EPROM compatibility.

MXIC's Flash technology reliably stores memory contents even after 100,000 erase and program cycles. The MXIC cell is designed to optimize the erase and programming mechanisms. In addition, the combination of advanced tunnel oxide processing and low internal electric fields for erase and programming operations produces reliable cycling. The MX29F002T/B uses a 5.0V  $\pm$  10% VCC supply to perform the High Reliability Erase and auto Program/Erase algorithms.

The highest degree of latch-up protection is achieved with MXIC's proprietary non-epi process. Latch-up protection is proved for stresses up to 100 milliamps on address and data pin from -1V to VCC + 1V.

## MX29F002/002N

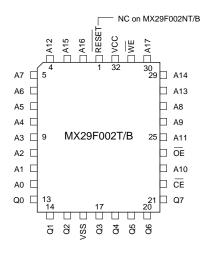

#### **PIN CONFIGURATIONS**

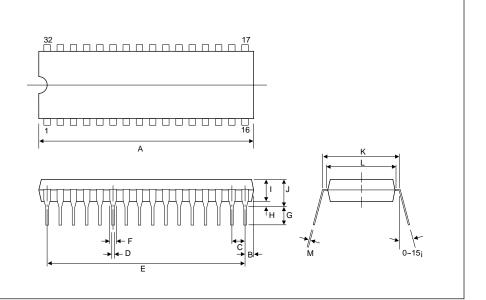

#### **32 PDIP**

| N     | NC on MX29F002NT/B |               |    |               |  |  |  |  |  |  |  |  |

|-------|--------------------|---------------|----|---------------|--|--|--|--|--|--|--|--|

| RESET | 1                  | $\overline{}$ | 32 | b vcc         |  |  |  |  |  |  |  |  |

| A16 🗆 | 2                  |               | 31 | D WE          |  |  |  |  |  |  |  |  |

| A15 🗆 | 3                  |               | 30 | 🗆 A17         |  |  |  |  |  |  |  |  |

| A12 🗆 | 4                  |               | 29 | 🗅 A14         |  |  |  |  |  |  |  |  |

| A7 🗆  | 5                  |               | 28 | 🗖 A13         |  |  |  |  |  |  |  |  |

| A6 🗆  | 6                  | 9             | 27 | 🗆 A8          |  |  |  |  |  |  |  |  |

| A5 🗆  | 7                  | MX29F002T/B   | 26 | 🗆 A9          |  |  |  |  |  |  |  |  |

| A4 🗆  | 8                  | 8             | 25 | □ <u>A1</u> 1 |  |  |  |  |  |  |  |  |

| A3 🗆  | 9                  | Ц6            | 24 |               |  |  |  |  |  |  |  |  |

| A2 🗆  | 10                 | Š             | 23 | 🗆 A10         |  |  |  |  |  |  |  |  |

| A1 🗆  | 11                 | ŝ             | 22 |               |  |  |  |  |  |  |  |  |

| A0 🗆  | 12                 |               | 21 | 🗖 Q7          |  |  |  |  |  |  |  |  |

| Q0 🗆  | 13                 |               | 20 | 🗖 Q6          |  |  |  |  |  |  |  |  |

| Q1 🗆  | 14                 |               | 19 | 🗖 Q5          |  |  |  |  |  |  |  |  |

| Q2 🗆  | 15                 |               | 18 | 🗖 Q4          |  |  |  |  |  |  |  |  |

| GND 🗆 | 16                 |               | 17 | 🗖 Q3          |  |  |  |  |  |  |  |  |

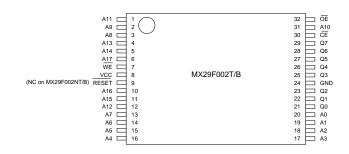

#### 32 PLCC

## **PIN DESCRIPTION**

| SYMBOL | PIN NAME                                 |

|--------|------------------------------------------|

| A0~A17 | Address Input                            |

| Q0~Q7  | Data Input/Output                        |

| CE     | Chip Enable Input                        |

| WE     | Write Enable Input                       |

| RESET  | Hardware Reset Pin/Sector Protect Unlock |

| ŌĒ     | Output Enable Input                      |

| VCC    | Power Supply Pin (+5V)                   |

| GND    | Ground Pin                               |

## 32 TSOP (TYPE 1)

(NORMAL TYPE)

#### **BLOCK STRUCTURE**

| A 1 7 ~ A 0                |                            |

|----------------------------|----------------------------|

| 3 F F F F H<br>3 B F F F H | 16 K-BYTE<br>(BOOT SECTOR) |

|                            | 8 K-BYTE                   |

| 3 9 F F F H                | 8 K-BYTE                   |

| 37FFFH                     | 32 K-BYTE                  |

| 2 F F F F H<br>1 F F F F H | 64 K-BYTE                  |

| 0 F F F F H                | 64 K-BYTE                  |

| 00000H                     | 64 K-BYTE                  |

| 0000011                    |                            |

#### MX29F002T Sector Architecture

| A 1 7 ~ A 0 |                            |

|-------------|----------------------------|

| 3 F F F F H |                            |

| 2 F F F F H | 64 K-BYTE                  |

| 1 F F F F H | 64 K-BYTE                  |

| 1 F F F F H | 64 K-BYTE                  |

| 0 F F F F H |                            |

| 07 F F F H  | 32 K-BYTE                  |

| •••••       | 8 K-BYTE                   |

| 0 5 F F F H | 8 K-BYTF                   |

| 0 3 F F F H | • · · · · · · · · ·        |

| 00000H      | 16 K-BYTE<br>(BOOT SECTOR) |

MX29F002B Sector Architecture

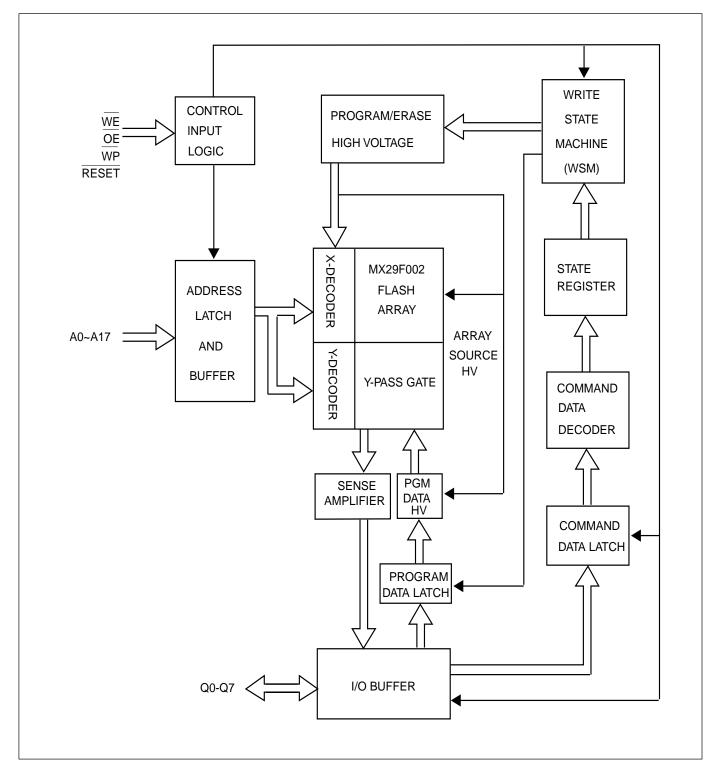

## **BLOCK DIAGRAM**

## **AUTOMATIC PROGRAMMING**

The MX29F002T/B is byte programmable using the Automatic Programming algorithm. The Automatic Programming algorithm does not require the system to time out or verify the data programmed. The typical chip programming time of the MX29F002T/B at room temperature is less than 2 seconds.

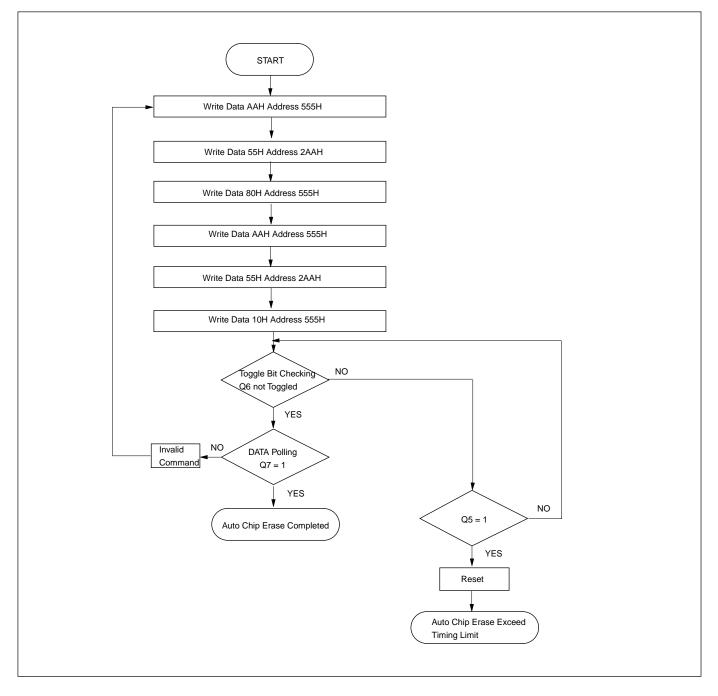

## AUTOMATIC CHIP ERASE

Typical erasure at room temperature is accomplished in less than two second. The device is erased using the Automatic Erase algorithm. The Automatic Erase algorithm automatically programs the entire array prior to electrical erase. The timing and verification of electrical erase are internally controlled by the device.

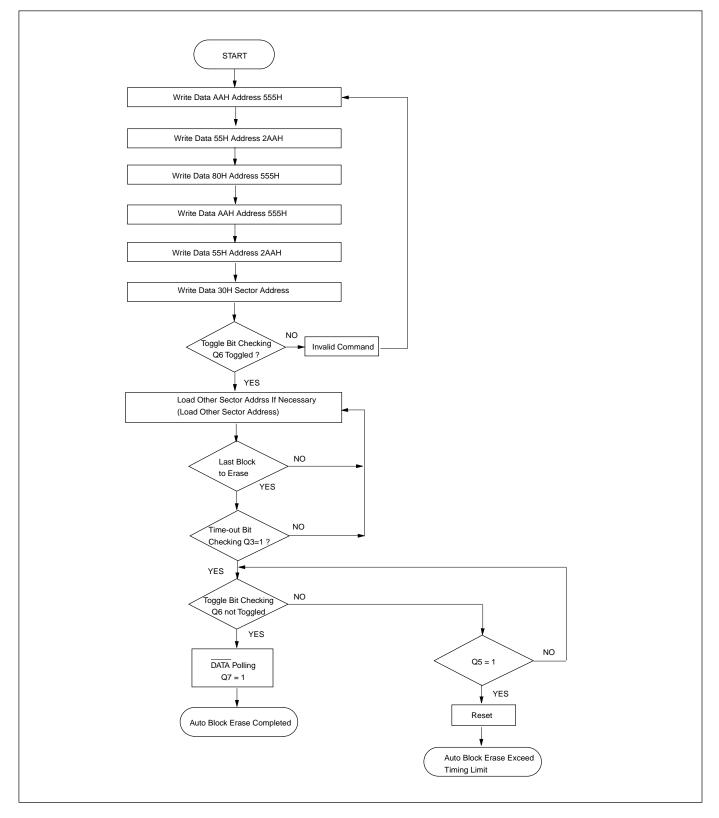

## AUTOMATIC BLOCK ERASE

The MX29F002T/B is block(s) erasable using MXIC's Auto Block Erase algorithm. Block erase modes allow blocks of the array to be erased in one erase cycle. The Automatic Block Erase algorithm automatically programs the specified block(s) prior to electrical erase. The timing and verification of electrical erase are internally controlled by the device.

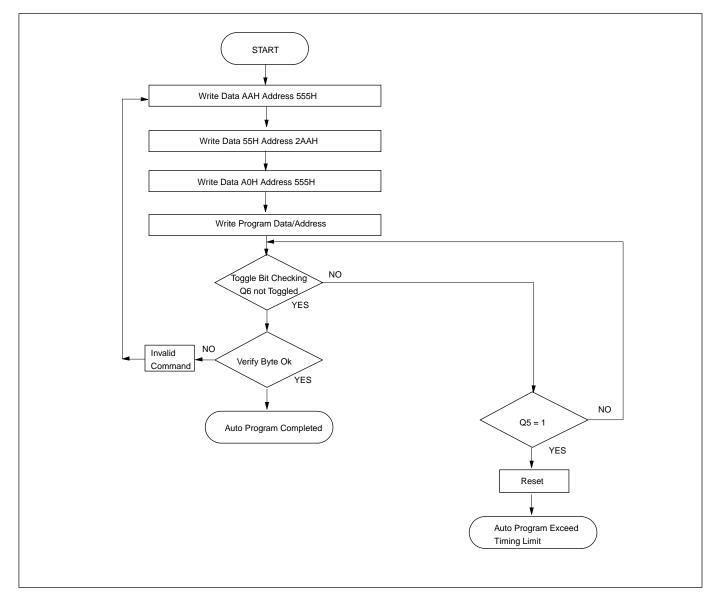

## AUTOMATIC PROGRAMMING ALGORITHM

MXIC's Automatic Programming algorithm requires the user to only write a program set-up commands include 2 unlock arite cycle and A0H and a program command (program data and address). The device automatically times the programming pulse width, verifies the program, and counts the number of sequences. A status bit similar to DATA polling and a-status bit toggling between consecutive read cycles, provides feedback to the user as to the status of the programming operation.

## AUTOMATIC ERASE ALGORITHM

MXIC's Automatic Erase algorithm requires the user to write commands to the command register using standard microprocessor write timings. The device will automatically pre-program and verify the entire array. Then the device automatically times the erase pulse width, verifies the erase, and counts the number of sequences. A status bit similar to DATA polling and status bit toggling between consecutive read cycles provides feedback to the user as to the status of the programming operation.

Commands are written to the command register using standard microprocessor write timings. Register contents serve as inputs to an internal state-machine which controls the erase and programming circuitry. During write cycles, the command register internally latches address and data needed for the programming and erase operations. During a system write cycle, addresses are latched on the falling edge, and data are latched on the rising edge of WE.

MXIC's Flash technology combines years of EPROM experience to produce the highest levels of quality, reliability, and cost effectiveness. The MX29F002T/B electrically erases all bits simultaneously using Fowler-Nordheim tunneling. The bytes are programmed one byte at a time using the EPROM programming mechanism of hot electron injection.

During a program cycle, the state-machine will control the program sequences and command register will not respond to any command set. During a Sector Erase cycle, the command register will only respond to Erase Suspend command. After Erase Suspend is completed, the device stays in read mode. After the state machine has completed its task, it will allow the command register to respond to its full command set.

## TABLE1. SOFTWARE COMMAND DEFINITIONS

| Command              | Bus   | First<br>Cyc |      |      | nd Bus<br>/cle |      | l Bus<br>cle | Fourt<br>Cy |      | Fifth B<br>Cycle |      | Sixth<br>Cyc |      |

|----------------------|-------|--------------|------|------|----------------|------|--------------|-------------|------|------------------|------|--------------|------|

|                      | Cycle | Addr         | Data | Addr | Data           | Addr | Data         | Addr        | Data | Addr             | Data | Addr         | Data |

| Reset/Read           | 1     | ХХХН         | F0H  |      |                |      |              |             |      |                  |      |              |      |

| Reset/Read           | 4     | 555H         | ААН  | 2AAH | 55H            | 555H | F0H          | RA          | RD   |                  |      |              |      |

| Read Silicon ID      | 4     | 555H         | AAH  | 2AAH | 55H            | 555H | 90H          | ADI         | DDI  |                  |      |              |      |

| Sector Protect       | 4     | 555H         | AAH  | 2AAH | 55H            | 555H | 90H          | SA          | 00H  |                  |      |              |      |

| Verification         |       |              |      |      |                |      |              | x02         | 01H  |                  |      |              |      |

| Porgram              | 4     | 555H         | AAH  | 2AAH | 55H            | 555H | A0H          | PA          | PD   |                  |      |              |      |

| Chip Erase           | 6     | 555H         | AAH  | 2AAH | 55H            | 555H | 80H          | 555H        | ААН  | 2AAH             | 55H  | 555H         | 10H  |

| Sector Erase         | 6     | 555H         | AAH  | 2AAH | 55H            | 555H | 80H          | 555H        | AAH  | 2AAH             | 55H  | SA           | 30Н  |

| Sector Erase Suspend | 1     | XXXH         | B0H  |      |                |      |              |             |      |                  |      |              |      |

| Sector Erase Resume  | 1     | XXXH         | 30H  |      |                |      |              |             |      |                  |      |              |      |

| Unlock for sector    | 6     | 555H         | AAH  | 2AAH | 55H            | 555H | 80H          | 555H        | AAH  | 2AAH             | 55H  | 555H         | 20H  |

| protect/unprotect    |       |              |      |      |                |      |              |             |      |                  |      |              |      |

Note:

1. ADI = Address of Device identifier; A1=0,A0 =0 for manufacture code,A1=0, A0 =1 for device code (Refer to Table 3).

DDI = Data of Device identifier : C2H for manufacture code, 00B0h/0034h for device code.

X = X can be VIL or VIH

RA=Address of memory location to be read.

RD=Data to be read at location RA.

- 2. PA = Address of memory location to be programmed.

- PD = Data to be programmed at location PA.

- SA = Address to the sector to be erased.

- 3. The system should generate the following address patterns: 555H or 2AAH to Address A0~A10. Address bit A11~A17=X=Don't care for all address commands except for Program Address (PA) and Sector Address (SA). Write Sequence may be initiated with A11~A17 in either state.

- 4.For Sector Protect Verification Operation : If read out data is 01H, it means the sector has been protected. If read out data is 00H, it means the sector is still not being protected.

## **COMMAND DEFINITIONS**

Device operations are selected by writing specific address and data sequences into the command register. Writing incorrect address and data values or writing them in the improper sequence will reset the device to the read mode. Table 1 defines the valid register command sequences. Note that the Erase Suspend (B0H) and Erase Resume (30H) commands are valid only while the Sector Erase operation is in progress. Either of the two reset command sequences will reset the device(when applicable).

5

#### TABLE 2. MX29F002T/B BUS OPERATION

| Pins                            | CE | OE                  | WE | A0 | A1 | A6 | A9                  | Q0~Q7               |

|---------------------------------|----|---------------------|----|----|----|----|---------------------|---------------------|

| Mode                            |    |                     |    |    |    |    |                     |                     |

| Read Silicon ID                 | L  | L                   | н  | L  | L  | х  | V <sub>ID</sub> (2) | C2H                 |

| Manfacturer Code(1)             |    |                     |    |    |    |    |                     |                     |

| Read Silicon ID                 | L  | L                   | Н  | Н  | L  | Х  | V <sub>ID</sub> (2) | B0h/34h             |

| Device Code(1)                  |    |                     |    |    |    |    |                     |                     |

| Read                            | L  | L                   | н  | A0 | A1 | A6 | A9                  | D <sub>OUT</sub>    |

| Standby                         | Н  | Х                   | х  | х  | Х  | Х  | Х                   | HIGH Z              |

| Output Disable                  | L  | Н                   | Н  | х  | Х  | Х  | х                   | HIGH Z              |

| Write                           | L  | н                   | L  | A0 | A1 | A6 | A9                  | D <sub>IN</sub> (3) |

| Sector Protect with 12V         | L  | V <sub>ID</sub> (2) | L  | х  | Х  | L  | V <sub>ID</sub> (2) | Х                   |

| system(6)                       |    |                     |    |    |    |    |                     |                     |

| Chip Unprotect with 12V         | L  | V <sub>ID</sub> (2) | L  | х  | х  | н  | V <sub>ID</sub> (2) | x                   |

| system(6)                       |    |                     |    |    |    |    |                     |                     |

| Verify Sector Protect           | L  | L                   | н  | х  | Н  | х  | V <sub>ID</sub> (2) | Code(5)             |

| with 12V system                 |    |                     |    |    |    |    |                     |                     |

| Sector Protect without 12V      | L  | н                   | L  | х  | Х  | L  | н                   | Х                   |

| system (6)                      |    |                     |    |    |    |    |                     |                     |

| Chip Unprotect without 12V      | L  | н                   | L  | Х  | Х  | н  | н                   | Х                   |

| system (6)                      |    |                     |    |    |    |    |                     |                     |

| Verify Sector Protect/Unprotect | L  | L                   | Н  | Х  | Н  | х  | н                   | Code(5)             |

| without 12V system (7)          |    |                     |    |    |    |    |                     |                     |

| Reset                           | Х  | х                   | х  | х  | х  | х  | х                   | HIGH Z              |

#### NOTES:

1. Manufacturer and device codes may also be accessed via a command register write sequence. Refer to Table 1.

- 2. VID is the Silicon-ID-Read high voltage, 11.5V to 12.5V.

- 3. Refer to Table 1 for valid Data-In during a write operation.

- 4. X can be VIL or VIH.

- 5. Code=00H means unprotected.

- Code=01H means protected.

- A17~A13=Sector address for sector protect.

- 6. Refer to sector protect/unprotect algorithm and waveform.

- Must issue "unlock for sector protect/unprotect" command before "sector protect/unprotect without 12V system" command.

- 7. The "verify sector protect/unprotect without 12V sysytem" is only following "Sector protect/unprotect without 12V system" command.

#### **READ/RESET COMMAND**

The read or reset operation is initiated by writing the read/ reset command sequence into the command register. Microprocessor read cycles retrieve array data. The device remains enabled for reads until the command register contents are altered.

If program-fail or erase-fail happen, the write of F0H will reset the device to abort the operation. A valid command must then be written to place the device in the desired state.

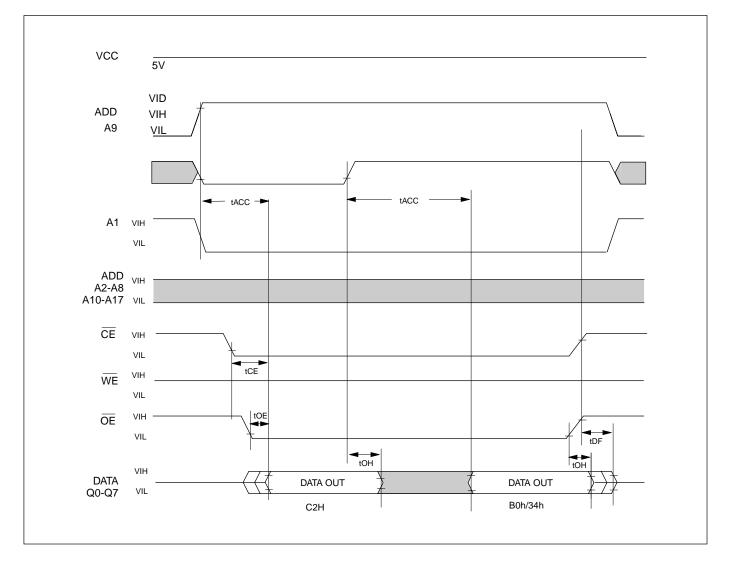

## SILICON-ID-READ COMMAND

Flash memories are intended for use in applications where the local CPU alters memory contents. As such, manufacturer and device codes must be accessible while the device resides in the target system. PROM programmers typically access signature codes by raising A9 to a high voltage. However, multiplexing high voltage onto address lines is not generally desired system design practice.

The MX29F002T/B contains a Silicon-ID-Read operation to supplement traditional PROM programming methodology. The operation is initiated by writing the read silicon ID command sequence into the command register. Following the command write, a read cycle with A1=VIL, A0=VIL retrieves the manufacturer code of C2H. A read cycle with A1=VIL, A0=VIH returns the device code of B0h for MX29F002T, 34h for MX29F002B.

## SET-UP AUTOMATIC CHIP/BLOCK ERASE COMMANDS

Chip erase is a six-bus cycle operation. There are two "unlock" write cycles. These are followed by writing the "set-up" command 80H. Two more "unlock" write cycles are then followed by the chip erase command 10H.

The Automatic Chip Erase does not require the device to be entirely pre-programmed prior to executing the Automatic Chip Erase. Upon executing the Automatic Chip Erase, the device will automatically program and verify the entire memory for an all-zero data pattern. When the device is automatically verified to contain an all-zero pattern, a self-timed chip erase and verify begin. The erase and verify operations are completed when the data on Q7 is "1" at which time the device returns to the Read mode. The system is not required to provide any control or timing during these operations.

When using the Automatic Chip Erase algorithm, note that the erase automatically terminates when adequate erase margin has been achieved for the memory array(no erase verify command is required).

If the Erase operation was unsuccessful, the data on Q5 is "1"(see Table 4), indicating the erase operation exceed internal timing limit.

The automatic erase begins on the rising edge of the last  $\overline{\text{WE}}$  pulse in the command sequence and terminates when the data on Q7 is "1" and the data on Q6 stops toggling for two consecutive read cycles, at which time the device returns to the Read mode.

| Pi                | ns A | ) A1  | Q7 | Q6 | Q5 | Q4 | Q3 | Q2 | Q1 | QO | Code(Hex)Code     |

|-------------------|------|-------|----|----|----|----|----|----|----|----|-------------------|

|                   |      |       |    |    |    |    |    |    |    |    |                   |

| Manufacture code  | VI   |       | 1  | 1  | 0  | 0  | 0  | 0  | 1  | 0  | C2H               |

| Device code       | VI   | I VIL | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 0  | B0h               |

| for MX29F002T     |      |       |    |    |    |    |    |    |    |    |                   |

| Device code       | VI   | I VIL | 0  | 0  | 1  | 1  | 0  | 1  | 0  | 0  | 34h               |

| for MX29F002B     |      |       |    |    |    |    |    |    |    |    |                   |

| Sector Protection | х    | VIH   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 01H (Protected)   |

| Verification      | X    | VIH   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 00H (Unprotected) |

## TABLE 3. EXPANDED SILICON ID CODE

# SET-UP AUTOMATIC BLOCK ERASE COMMANDS

The Automatic Block Erase does not require the device to be entirely pre-programmed prior to executing the Automatic Set-up Block Erase command and Automatic Block Erase command. Upon executing the Automatic Block Erase command, the device will automatically program and verify the block(s) memory for an all-zero data pattern. The systemdoes not require to provide any control or timing during these operations.

When the block(s) is automatically verified to contain an all-zero pattern, a self-timed block erase and verification begin. The erase and verification operations are complete when the data on Q7 is "1" and the data on Q6 stops toggling for two consecutive read cycles, at which time the device returns to the Read mode. The system does not required to provide any control or timing during these operations.

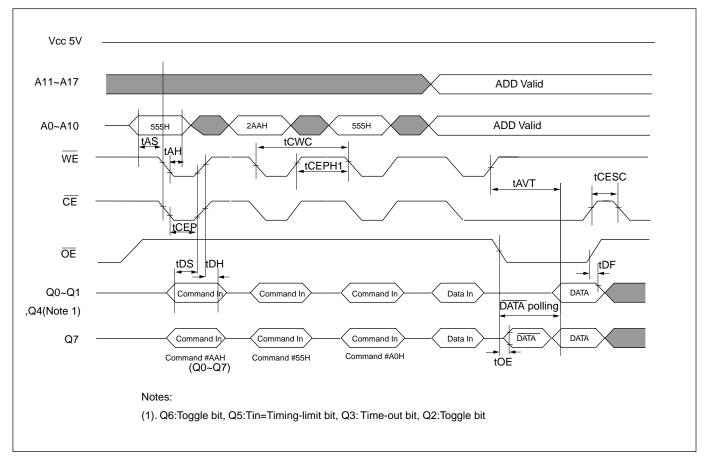

When using the Automatic Block Erase algorithm, note that the erase automatically terminates when adequate erase margin has been achieved for the memory array (no erase verify command is required). Sector erase is a sixbus cycle operation. There are two "unlock" write cycles. These are followed by writing the set-up command-80H. Two more "unlock" write cycles are then followed by the sector erase command-30H. The sector address is latched on the falling edge of WE, while the command(data) is latched on the rising edge of WE. Block addresses selected are loaded into internal register on the sixth falling edge of  $\overline{WE}$ . Each successive block load cycle started by the falling edge of  $\overline{WE}$  must begin within 30ms from the rising edge of the preceding  $\overline{WE}$ . Otherwise, the loading period ends and internal auto block erase cycle starts. (Monitor Q3 to determine if the sector erase timer window is still open, see section Q3, Sector Erase Timer.) Any command other than Block Erase (30H) or Erase Suspend (BOH) during the time-out period resets the device to read mode.

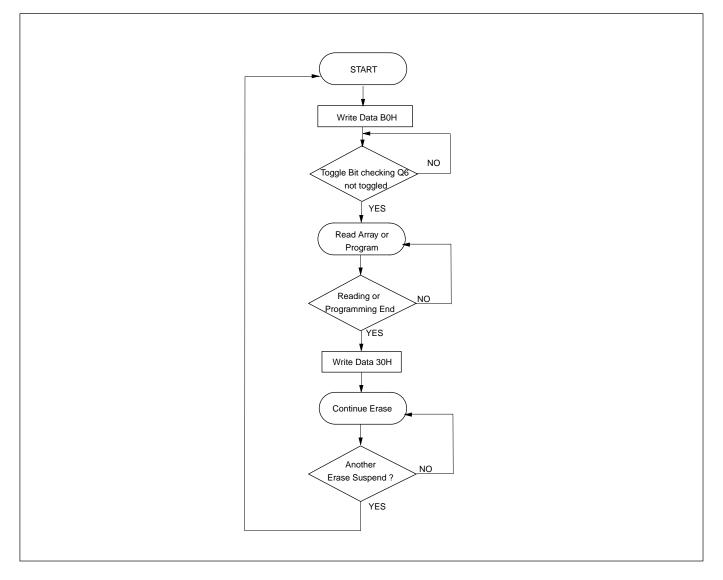

#### **ERASE SUSPEND**

This command is only valid while the state machine is executing Automatic Block Erase operation, and therefore will only be responded during Automatic/Block Erase operation. Writing the Erase Suspend command during the Block Erase time-out immediately terminates the timeout period and suspends the erase operation. After this command has been executed, the command register will initiate erase suspend mode. The state machine will return to read mode automatically after suspend is ready. At this time, state machine only allows the command register to respond to the Read Memory Array, Erase Resume and Program commands. The system can determine the status of the program operation using the Q7 or Q6 status bits, just as in the standard program operation. After an erase-suspendend program operation is complete, the system can once again read array data within non-suspended blocks.

#### **Table 4. Write Operation Status**

|                    | Mode                           | Q7       | Q6        | Q5       | Q3   | Q2        |

|--------------------|--------------------------------|----------|-----------|----------|------|-----------|

|                    |                                | (Note 1) |           | (Note 2) |      | (Note 1)  |

| Standard Mode      | Auto Program Algorithm         | Q7       | Toggle    | 0        | N/A  | No Toggle |

|                    | Auto Erase Algorithm           | 0        | Toggle    | 0        | 1    | Toggle    |

| Exceed Time Limits | Auto Program                   | Q7       | Toggle    | 1        | 0    | No Toggle |

|                    | Auto Sector/Chip Erase         | 0        | Toggle    | 1        | 0    | N/A       |

| Erase Suspend Mode | Reading within Erase Suspended | 1        | No toggle | 0        | N/A  | Toggle    |

|                    | Sector                         |          |           |          |      |           |

|                    | Reading within Non-Erase       | Data     | Data      | Data     | Data | Data      |

|                    | Suspended Sector               |          |           |          |      |           |

|                    | Earse-Suspend-Program          | Q7       | Toggle    | 0        | N/A  | N/A       |

Note:

1. Q7 and Q2 require a valid address when reading status information. Refer to the appropriate subsection for further details.

2. Q5 switches to '1' when an Auto Program or Auto Erase operation has exceeded the maximum timing limits.

See "Q5:Exceeded Timing Limits " for more information.

## ERASE RESUME

This command will cause the command register to clear the suspend state and return back to Sector Erase mode but only if an Erase Suspend command was previously issued. Erase Resume will not have any effect in all other conditions.Another Erase Suspend command can be written after the chip has resumed erasing.

## SET-UP AUTOMATIC PROGRAM COMMANDS

To initiate Automatic Program mode, a three-cycle command sequence is required. There are two "unlock" write cycles. These are followed by writing the Automatic Program command A0H.

Once the Automatic Program command is initiated, the next  $\overline{WE}$  pulse causes a transition to an active programming operation. Addresses are latched on the falling edge, and data are internally latched on the rising edge of the  $\overline{WE}$  pulse. The rising edge of  $\overline{WE}$  also begins the programming operation. The system does not require to provide further controls or timings. The device will automatically provide an adequate internally generated program pulse and verify margin.

If the program opetation was unsuccessful, the data on Q5 is "1", indicating the program operation exceed internal timing limit. The automatic programming operation is completed when the data read on Q6 stops toggling for two consecutive read cycles and the data on Q7 and Q6 are equivalent to data written to these two bits, at which time the device returns to the Read mode(no program verify command is required).

## WRITE OPERATION STATUS

## **DATA POLLING-Q7**

The MX29F002T/B also features Data Polling as a method to indicate to the host system that the Automatic Program or Erase algorithms are either in progress or completed.

While the Automatic Programming algorithm is in operation, an attempt to read the device will produce the complement data of the data last written to Q7. Upon completion of the Automatic Program Algorithm an attempt to read the device will produce the true data last written to Q7. The Data Polling feature is valid after the rising edge of the second WE pulse of the two write pulse sequences. While the Automatic Erase algorithm is in operation, Q7 will read "0" until the erase operation is competed. Upon completion of the erase operation, the data on Q7 will read "1". The Data Polling feature is valid after the rising edge of the secone WE pulse of two write pulse sequences.

The Data Polling feature is active during Automatic Program/Erase algorithm or sector erase time-out.(see section Q3 Sector Erase Timer)

## Q6:Toggle BIT I

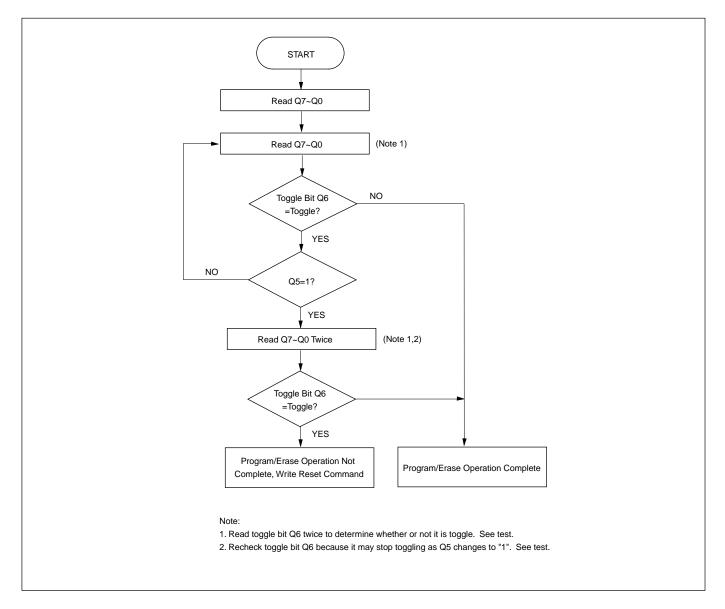

The MX29F002T/B features a "Toggle Bit" as a method to indicate to the host system that the Auto Program/Erase algorithms are either in progress or completed.

During an Automatic Program or Erase algorithm operation, successive read cycles to any address cause Q6 to toggle. The system may use either OE or CE to control the read cycles. When the operation is complete, Q6 stops toggling.

After an erase command sequence is written, if all sectors selected for erasing are protected, Q6 toggles and returns to reading array data. If not all selected sectors are protected, the Automatic Erase algorithm erases the unprotected sectors, and ignores the selected sectors that are protected.

The system can use Q6 and Q2 together to determine whether a sector is actively erasing or is erase suspended. When the device is actively erasing (that is, the Automatic Erase algorithm is in progress), Q6 toggling. When the device enters the Erase Suspend mode, Q6 stops toggling. However, the system must also use Q2 to determine which sectors are erasing or erase-suspended. Alternatively, the system can use Q7(see the subsection on Q7:Data Polling).

If a program address falls within a protected sector, Q6 toggles for approximately 2 us after the program command sequence is written, then returns to reading array data.

Q6 also toggles during the erase-suspend-program mode, and stops toggling once the Automatic Program algorithm is complete.

The Write Operation Status table shows the outputs for Toggle Bit I on Q6. Refer to the toggle bit algorithmg.

## Q2:Toggle Bit II

The "Toggle Bit II" on Q2, when used with Q6, indicates whether a particular sector is actively eraseing (that is, the Automatic Erase alorithm is in process), or whether that sector is erase-suspended. Toggle Bit I is valid after the rising edge of the final  $\overline{WE}$  pulse in the command sequence.

Q2 toggles when the system reads at addresses within those sectors that have been selected for erasure. (The system may use either  $\overline{OE}$  or  $\overline{CE}$  to control the read cycles.) But Q2 cannot distinguish whether the sector is actively erasing or is erase-suspended. Q6, by comparison, indicates whether the device is actively erasing, or is in Erase Suspend, but cannot distinguish which sectors are selected for erasure. Thus, both status bits are required for sectors and mode information. Refer to Table 4 to compare outputs for Q2 and Q6.

## Reading Toggle Bits Q6/ Q2

Refer to the toggle bit algorithm for the following discussion. Whenever the system initially begins reading toggle bit status, it must read Q7-Q0 at least twice in a row to determine whether a toggle bit is toggling. Typically, the system would note and store the value of the toggle bit after the first read. After the second read, the system would compare the new value of the toggle bit with the first. If the toggle bit is not toggling, the device has completed the program or erase operation. The system can read array data on Q7-Q0 on the following read cycle.

However, if after the initial two read cycles, the system determines that the toggle bit is still toggling, the system also should note whether the value of Q5 is high (see the section on Q5). If it is, the system should then determine again whether the toggle bit is toggling, since the toggle bit may have stopped toggling just as Q5 went high. If the toggle bit is no longer toggling, the device has successfully completed the program or erase operation. If it is still toggling, the device did not complete the operation successfully, and the system must write the reset command to return to reading array data.

The remaining scenario is that system initially determines that the toggle bit is toggling and Q5 has not gone high. The system may continue to monitor the toggle bit and Q5 through successive read cycles, determining the status as described in the previous paragraph. Alternatively, it may choose to perform other system tasks. In this case, the system must start at the beginning of the algorithm when it returns to determine the status of the operation(top of the toggle bit algorithm flow chart).

#### Q5

## **Exceeded Timing Limits**

Q5 will indicate if the program or erase time has exceeded the specified limits(internal pulse count). Under these conditions Q5 will produce a "1". This time-out condition which indicates that the program or erase cycle was not successfully completed. Data Polling and Toggle Bit are the only operating functions not of the device under this condition.

If this time-out condition occurs during sector erase operation, it specifies that a particular sector is bad and it may not be reused. However, other sectors are still functional and may be used for the program or erase operation. The device must be reset to use other sectors. Write the Reset command sequence to the device, and then execute program or erase command sequence. This allows the system to continue to use the other active sectors in the device.

If this time-out condition occurs during the chip erase operation, it specifies that the entire chip is bad or combination of sectors are bad.

If this time-out condition occurs during the byte programming operation, it specifies that the entire sector containing that byte is bad and this sector maynot be reused, (other sectors are still functional and can be reused).

The Q5 time-out condition may also appear if a user tries to program a non blank location without erasing. In this case the device locks out and never completes the Automatic Algorithm operation. Hence, the system never reads a valid data on Q7 bit and Q6 never stops toggling. Once the Device has exceeded timing limits, the Q5 bit will indicate a "1". Please note that this is not a device failure condition since the device was incorrectly used.

#### Q3

#### Sector Erase Timer

After the completion of the initial sector erase command sequence th sector erase time-out will begin. Q3 will remain low until the time-out is complete. Data Polling and Toggle Bit are valid after the initial sector erase command sequence.

If Data Polling or the Toggle Bit indicates the device has been written with a valid erase command, Q3 may be used to determine if the sector erase timer window is still open. If Q3 is high ("1") the internally controlled erase cycle has begun; attempts to write subsequent commands to the device will be ignored until the erase operation is completed as indicated by Data Polling or Toggle Bit. If Q3 is low ("0"), the device will accept additional sector erase commands. To insure the command has been accepted, the system software should check the status of Q3 prior to and following each subsequent sector erase command. If Q3 were high on the second status check, the command may not have been accepted.

## DATA PROTECTION

The MX29F002T/B is designed to offer protection against accidental erasure or programming caused by spurious system level signals that may exist during power transition. During power up the device automatically resets the state machine in the Read mode. In addition, with its control register architecture, alteration of the memory contents only occurs after successful completion of specific command sequences. The device also incorporates several features to prevent inadvertent write cycles resulting from VCC power-up and power-down transition or system noise.

## WRITE PULSE "GLITCH" PROTECTION

Noise pulses of less than 5ns(typical) on  $\overline{CE}$  or  $\overline{WE}$  will not initiate a write cycle.

### LOGICAL INHIBIT

Writing is inhibited by holding any one of  $\overline{OE} = VIL$ ,  $\overline{CE} = VIH$  or  $\overline{WE} = VIH$ . To initiate a write cycle  $\overline{CE}$  and  $\overline{WE}$  must be a logical zero while  $\overline{OE}$  is a logical one.

## POWER SUPPLY DECOUPLING

In order to reduce power switching effect, each device should have a 0.1 uF ceramic capacitor connected between its VCC and GND.

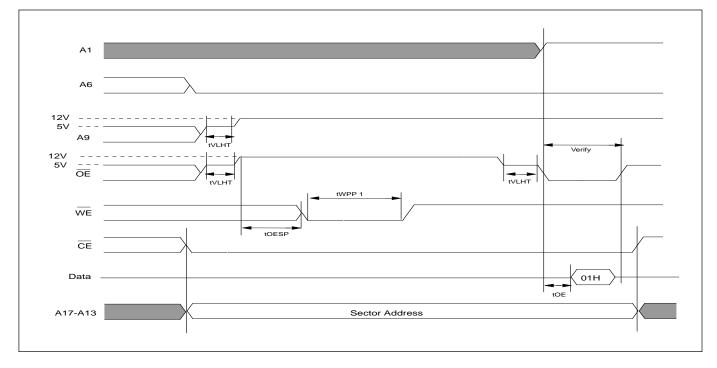

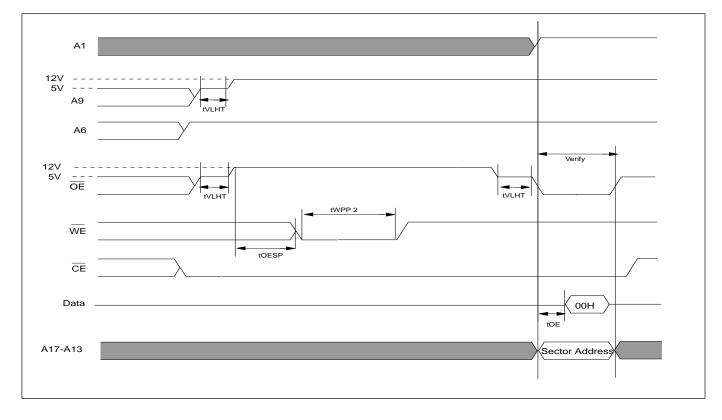

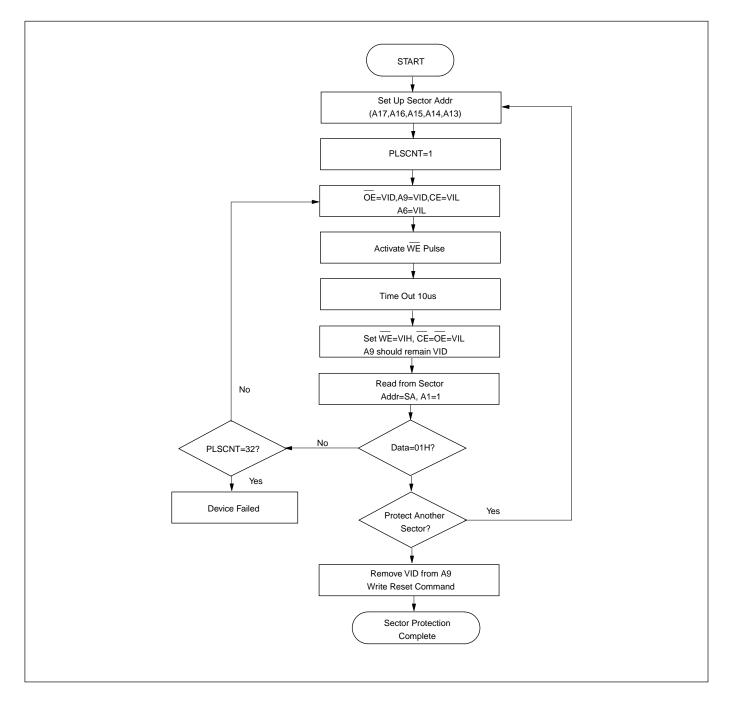

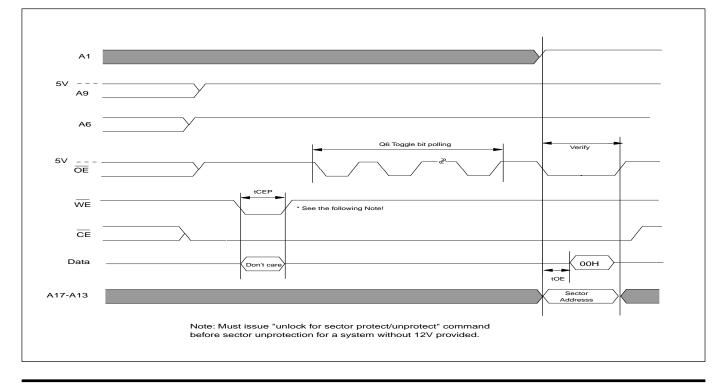

#### SECTOR PROTECTION WITH 12V SYSTEM

The MX29F002T/B features hardware sector protection. This feature will disable both program and erase operations for these sectors protected. To activate this mode, the programming equipment must force VID on address pin A9 and control pin  $\overrightarrow{OE}$ , (suggest VID = 12V) A6 = VIL and  $\overrightarrow{CE}$  = VIL.(see Table 2) Programming of the protection circuitry begins on the falling edge of the  $\overrightarrow{WE}$  pulse and is terminated on the rising edge. Please refer to sector protect algorithm and waveform.

To verify programming of the protection circuitry, the programming equipment must force VID on address pin A9 (with  $\overline{CE}$  and  $\overline{OE}$  at VIL and  $\overline{WE}$  at VIH. When A1=1, it will produce a logical "1" code at device output Q0 for a protected sector. Otherwise the device will produce 00H for the unprotected sector. In this mode, the addresses, except for A1, are in "don't care" state. Address locations with A1 = VIL are reserved to read manufacturer and device codes. (Read Silicon ID)

It is also possible to determine if the sector is protected in the system by writing a Read Silicon ID command. Performing a read operation with A1=VIH, it will produce a logical "1" at Q0 for the protected sector.

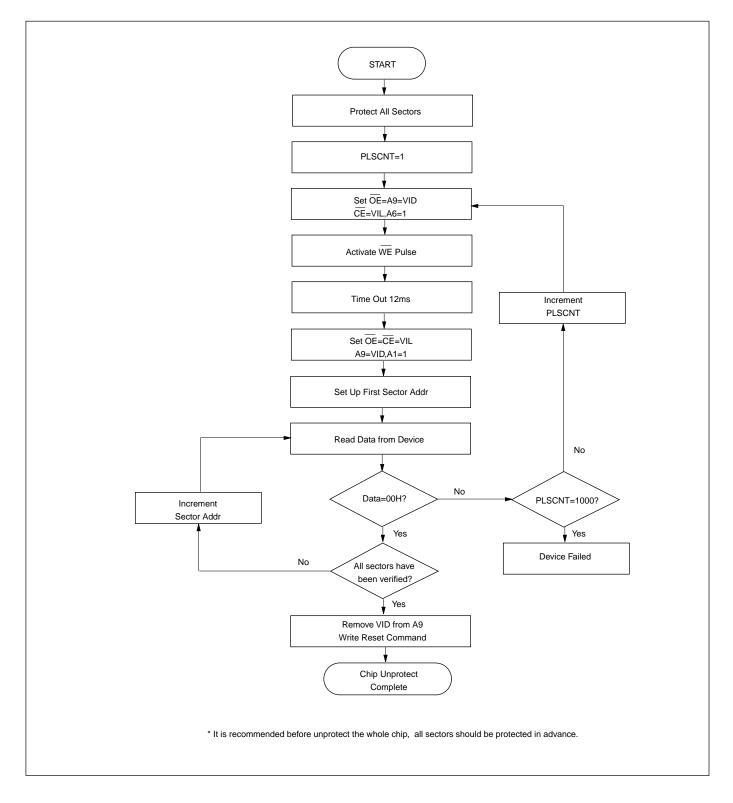

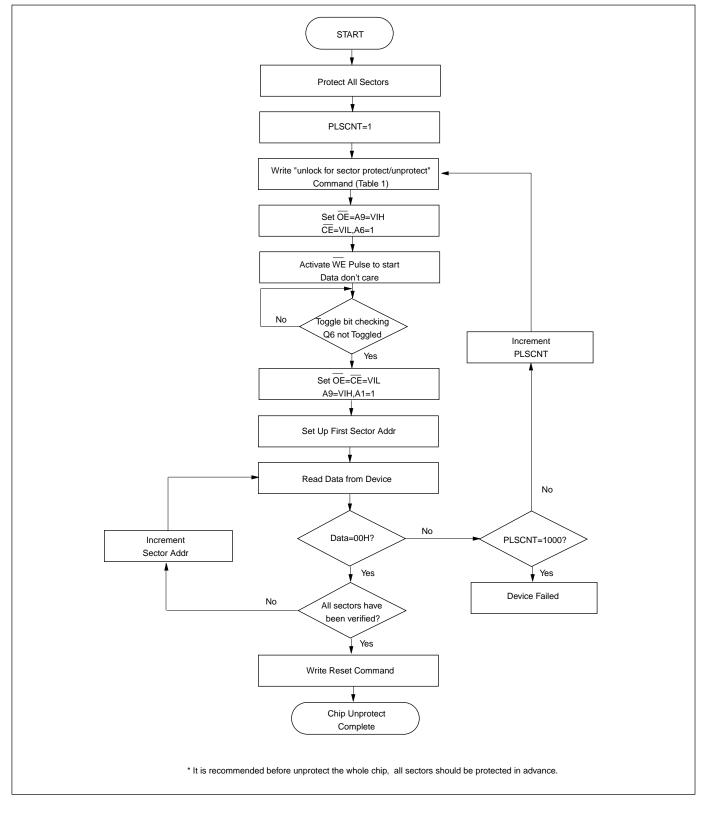

## CHIP UNPROTECT WITH 12V SYSTEM

The MX29F002T/B also features the chip unprotect mode, so that all sectors are unprotected after chip unprotect is completed to incorporate any changes in the code. It is recommended to protect all sectors before activating chip unprotect mode.

To activate this mode, the programming equipment must force VID on control pin  $\overline{OE}$  and address pin A9. The  $\overline{CE}$ pins must be set at VIL. Pins A6 must be set to VIH.(see Table 2) Refer to chip unprotect algorithm and waveform for the chip unprotect algorithm. The unprotection mechanism begins on the falling edge of the WE pulse and is terminated on the rising edge.

It is also possible to determine if the chip is unprotected in the system by writing the Read Silicon ID command. Performing a read operation with A1=VIH, it will produce 00H at data outputs(Q0-Q7) for an unprotected sector. It is noted that all sectors are unprotected after the chip unprotect algorithm is completed.

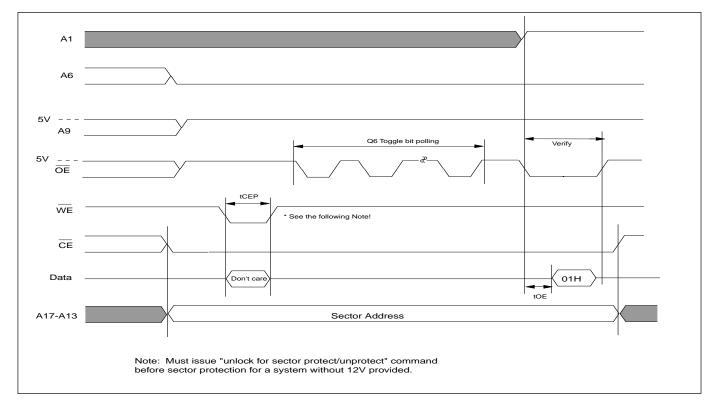

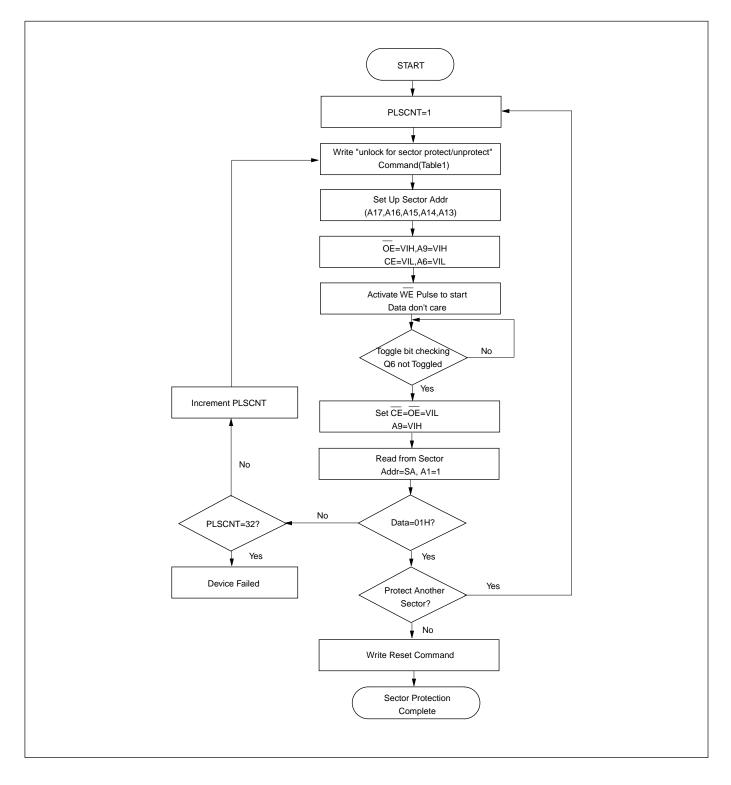

# SECTOR PROTECTION WITHOUT 12V SYSTEM

The MX29F002T/B also feature a hardware sector protection method in a system without 12V power suppply. The programming equipment do not need to supply 12 volts to protect sectors. The details are shown in sector protect algorithm and waveform.

## CHIP UNPROTECT WITHOUT 12V SYSTEM

The MX29F002T/B also feature a hardware chip unprotection method in a system without 12V power supply. The programming equipment do not need to supply 12 volts to unprotect all sectors. The details are shown in chip unprotect algorithm and waveform.

## **POWER-UP SEQUENCE**

The MX29F002T/B powers up in the Read only mode. In addition, the memory contents may only be altered after successful completion of a two-step command sequence. Vpp and Vcc power up sequence is not required.

## **ABSOLUTE MAXIMUM RATINGS**

| RATING                        | VALUE          |

|-------------------------------|----------------|

| Ambient Operating Temperature | 0°C to 70°C    |

| Storage Temperature           | -65°C to 125°C |

| Applied Input Voltage         | -0.5V to 7.0V  |

| Applied Output Voltage        | -0.5V to 7.0V  |

| VCC to Ground Potential       | -0.5V to 7.0V  |

| A9                            | -0.5V to 13.5V |

#### NOTICE:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended period may affect reliability.

#### NOTICE:

Specifications contained within the following tables are subject to change.

#### CAPACITANCE TA = 25°C, f = 1.0 MHz

| SYMBOL | PARAMETER          | MIN. | TYP | MAX. | UNIT | CONDITIONS |

|--------|--------------------|------|-----|------|------|------------|

| CIN    | Input Capacitance  |      |     | 8    | pF   | VIN = 0V   |

| COUT   | Output Capacitance |      |     | 12   | pF   | VOUT = 0V  |

#### **READ OPERATION**

#### DC CHARACTERISTICS TA = 0°C TO 70°C, VCC = 5V ± 10%

| SYMBOL | PARAMETER              | MIN.    | ТҮР   | MAX.      | UNIT | CONDITIONS                   |

|--------|------------------------|---------|-------|-----------|------|------------------------------|

| ILI    | Input Leakage Current  |         |       | 1         | mA   | VIN = GND to VCC             |

| ILO    | Output Leakage Current |         |       | 10        | mA   | VOUT = GND to VCC            |

| ISB1   | Standby VCC current    |         |       | 1         | mA   | CE = VIH                     |

| ISB2   |                        |         | 1     | 100       | mA   | $\overline{CE} = VCC + 0.3V$ |

| ICC1   | Operating VCC current  |         |       | 50        | mA   | IOUT = 0mA, f=1MHz           |

| ICC2   |                        |         |       | 70        | mA   | IOUT = 0mA, f=10MHz          |

| VIL    | Input Low Voltage      | -0.3(NO | ΓE 1) | 0.8       | V    |                              |

| VIH    | Input High Voltage     | 2.0     |       | VCC + 0.3 | V    |                              |

| VOL    | Output Low Voltage     |         |       | 0.45      | V    | IOL = 2.1mA                  |

| VOH    | Output High Voltage    | 2.4     |       |           | V    | IOH = -2mA                   |

#### NOTES:

- 1. VIL min. = -1.0V for pulse width is equal to or less than 50 ns.

- VIL min. = -2.0V for pulse width is equal to or less than 20 ns.

- 2. VIH max. = VCC + 1.5V for pulse width is equal to or less than 20 ns

- If VIH is over the specified maximum value, read operation cannot be guaranteed.

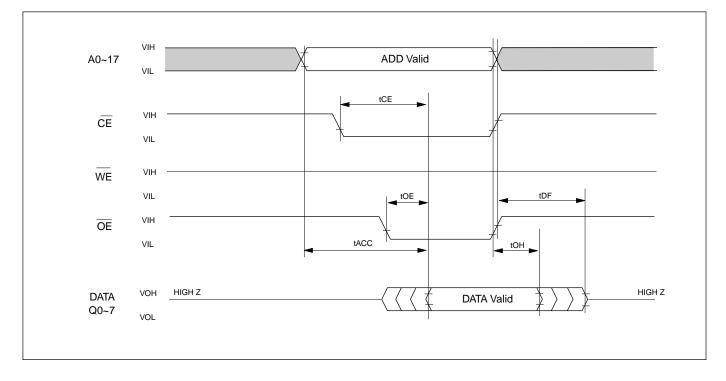

## AC CHARACTERISTICS TA = $0^{\circ}$ C to $70^{\circ}$ C, VCC = 5V ± 10%

|        |                                 | 29F002T/B-70 |      | 29F0 | 29F002T/B-90 |      | 29F002T/B-12 |      |            |

|--------|---------------------------------|--------------|------|------|--------------|------|--------------|------|------------|

| SYMBOL | PARAMETER                       | MIN.         | MAX. | MIN. | MAX.         | MIN. | MAX.         | UNIT | CONDITIONS |

| tACC   | Address to Output Delay         |              | 70   |      | 90           |      | 120          | ns   | CE=OE=VIL  |

| tCE    | CE to Output Delay              |              | 70   |      | 90           |      | 120          | ns   | OE=VIL     |

| tOE    | OE to Output Delay              |              | 30   |      | 40           |      | 50           | ns   | CE=VIL     |

| tDF    | OE High to Output Float (Note1) | 0            | 20   | 0    | 30           | 0    | 30           | ns   | CE=VIL     |

| tOH    | Address to Output hold          | 0            |      | 0    |              | 0    |              | ns   | CE=OE=VIL  |

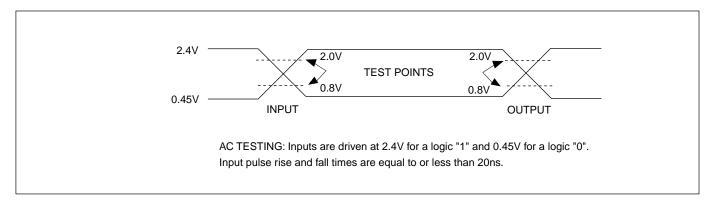

#### **TEST CONDITIONS:**

- Input pulse levels: 0.45V/2.4V

- Input rise and fall times: is equal to or less than 10ns

- Output load: 1 TTL gate + 35pF (Including scope and jig)

- Reference levels for measuring timing: 0.8V, 2.0V

#### NOTE:

1. tDF is defined as the time at which the output achieves the open circuit condition and data is no longer driven.

#### **READ TIMING WAVEFORMS**

## COMMAND PROGRAMMING/DATA PROGRAMMING/ERASE OPERATION

#### DC CHARACTERISTICS TA = $0^{\circ}$ C to $70^{\circ}$ C, VCC = $5V \pm 10\%$

| SYMBOL         | PARAMETER                 | MIN. | ТҮР | MAX. | UNIT | CONDITIONS              |

|----------------|---------------------------|------|-----|------|------|-------------------------|

| ICC1 (Read)    | Operating VCC Current     |      |     | 30   | mA   | IOUT=0mA, f=1MHz        |

| ICC2           |                           |      |     | 50   | mA   | IOUT=0mA, F=10MHz       |

| ICC3 (Program) | )                         |      |     | 50   | mA   | In Programming          |

| ICC4 (Erase)   |                           |      |     | 50   | mA   | In Erase                |

| ICCES          | VCC Erase Suspend Current |      | 2   |      | mA   | CE=VIH, Erase Suspended |

#### NOTES:

- 1. VIL min. = -0.6V for pulse width is equal to or less than 20ns.

- 2. If VIH is over the specified maximum value, programming operation cannot be guranteed.

- 3. ICCES is specified with the device de-selected. If the device is read during erase suspend mode, current draw is the sum of ICCES and ICC1 or ICC2.

- 4. All current are in RMS unless otherwise noted.

|        |                                        | 29F002T | /B-70 | 29F002  | T/B-90 | 29F002  | T/B-12 |      |            |

|--------|----------------------------------------|---------|-------|---------|--------|---------|--------|------|------------|

| SYMBOL | PARAMETER                              | MIN.    | MAX.  | MIN.    | MAX.   | MIN.    | MAX.   | UNIT | CONDITIONS |

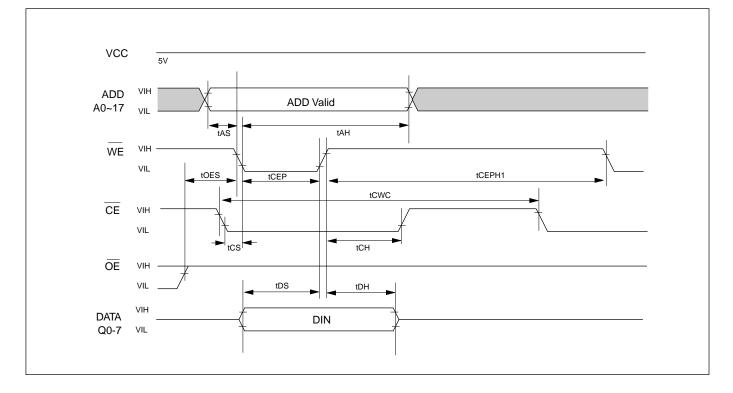

| tOES   | OE setup time                          | 50      |       | 50      |        | 50      |        | ns   |            |

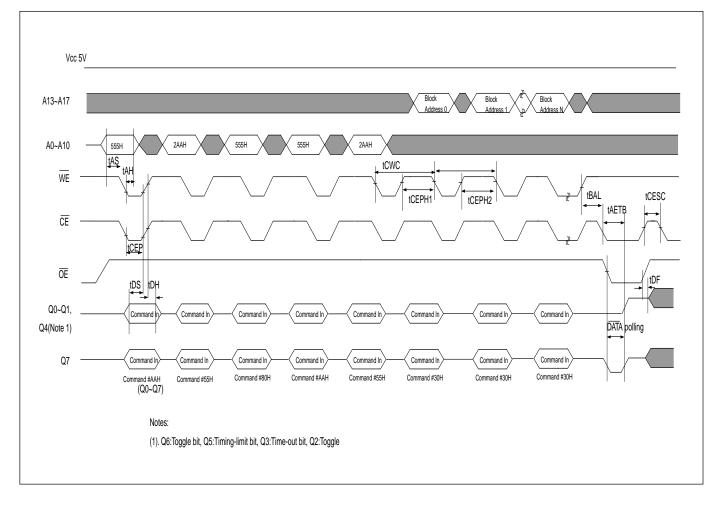

| tCWC   | Command programming cycle              | 70      |       | 90      |        | 120     |        | ns   |            |

| tCEP   | WE programming pulse width             | 35      |       | 45      |        | 50      |        | ns   |            |

| tCEPH1 | WE programming pluse width High        | 20      |       | 20      |        | 20      |        | ns   |            |

| tCEPH2 | WE programming pluse width High        | 20      |       | 20      |        | 20      |        | ns   |            |

| tAS    | Address setup time                     | 0       |       | 0       |        | 0       |        | ns   |            |

| tAH    | Address hold time                      | 45      |       | 45      |        | 50      |        | ns   |            |

| tDS    | Data setup time                        | 30      |       | 45      |        | 50      |        | ns   |            |

| tDH    | Data hold time                         | 0       |       | 0       |        | 0       |        | ns   |            |

| tCESC  | CE setup time before command write     | 0       |       | 0       |        | 0       |        | ns   |            |

| tDF    | Output disable time (Note 1)           | 3       | 30    |         | 40     |         | 40     | ns   |            |

| tAETC  | Total erase time in auto chip erase    | 2(TYP.) |       | 2(TYP.) |        | 2(TYP.) |        | S    |            |

| tAETB  | Total erase time in auto block erase   | 1(TYP.) |       | 1(TYP.) |        | 1(TYP.) |        | S    |            |

| tAVT   | Total programming time in auto verify  | 7       |       | 7       |        | 7       |        | us   |            |

|        | (Byte Program time)                    |         |       |         |        |         |        |      |            |

| tBAL   | Block address load time                | 80      |       | 80      |        | 80      |        | us   |            |

| tCH    | CE Hold Time                           | 0       |       | 0       |        | 0       |        | ns   |            |

| tCS    | CE setup to WE going low               | 0       |       | 0       |        | 0       |        | ns   |            |

| tVLHT  | Voltge Transition Time                 | 4       |       | 4       |        | 4       |        | us   |            |

| tOESP  | OE Setup Time to WE Active             | 4       |       | 4       |        | 4       |        | us   |            |

| tWPP1  | Write pulse width for sector protect   | 10      |       | 10      |        | 10      |        | us   |            |

| tWPP2  | Write pulse width for sector unprotect | 12      |       | 12      |        | 12      |        | ms   |            |

## AC CHARACTERISTICS TA = 0°C to 70°C, VCC = $5V \pm 10\%$

#### NOTES:

1. tDF defined as the time at which the output achieves the open circuit condition and data is no longer driven.

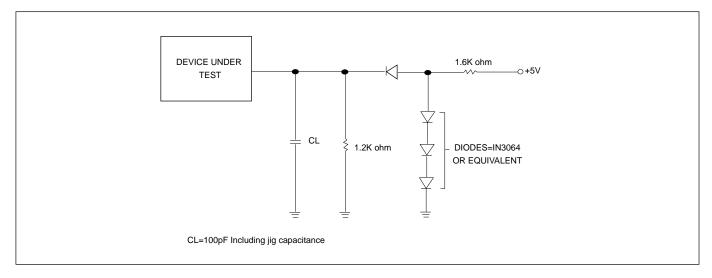

## SWITCHING TEST CIRCUITS

## SWITCHING TEST WAVEFORMS

## COMMAND WRITE TIMING WAVEFORM

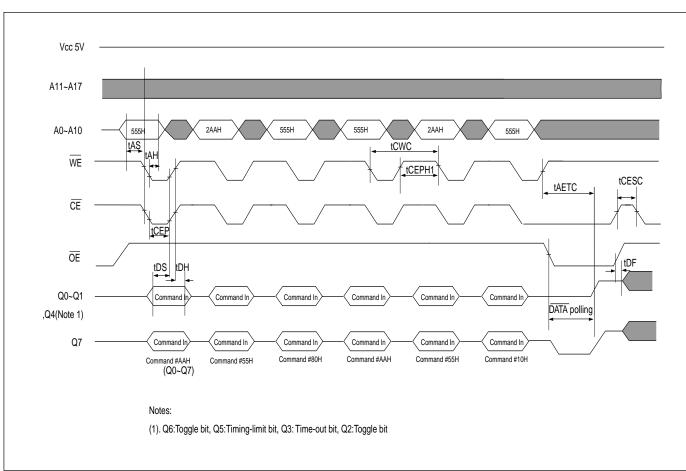

# AUTOMATIC PROGRAMMING TIMING WAVEFORM

One byte data is programmed. Verify in fast algorithm and additional programming by external control are not required because these operations are executed automatically by internal control circuit. Programming completion can be verified by DATA polling and toggle bit checking after automatic verification starts. Device outputs DATA during programming and DATA after programming on Q7.(Q6 is for toggle bit; see toggle bit, DATA polling, timing waveform)

## AUTOMATIC PROGRAMMING TIMING WAVEFORM

## AUTOMATIC PROGRAMMING ALGORITHM FLOWCHART

#### **TOGGLE BIT ALGORITHM**

# AUTOMATIC CHIP ERASE TIMING WAVEFORM

All data in chip are erased. External erase verify is not required because data is erased automatically by internal control circuit. Erasure completion can be verified by DATA polling and toggle bit checking after automatic erase starts. Device outputs 0 during erasure and 1 after erasure on Q7.(Q6 is for toggle bit; see toggle bit, DATA polling, timing waveform)

## AUTOMATIC CHIP ERASE TIMING WAVEFORM

## AUTOMATIC CHIP ERASE ALGORITHM FLOWCHART

# AUTOMATIC BLOCK ERASE TIMING WAVEFORM

Block data indicated by A13 to A17 are erased. External erase verification is not required because data are erased automatically by internal control circuit. Erasure completion can be verified by DATA polling and toggle bit

checking after automatic erase starts. Device outputs 0 during erasure and 1 after erasure on Q7.(Q6 is for toggle bit; see toggle bit, DATA polling, timing waveform)

## AUTOMATIC BLOCK ERASE TIMING WAVEFORM

## AUTOMATIC BLOCK ERASE ALGORITHM FLOWCHART

## ERASE SUSPEND/ERASE RESUME FLOWCHART

## TIMING WAVEFORM FOR SECTOR PROTECTION FOR SYSTEM WITH 12V

TIMING WAVEFORM FOR CHIP UNPROTECTION FOR SYSTEM WITH 12V

## SECTOR PROTECTION ALGORITHM FOR SYSTEM WITH 12V

## CHIP UNPROTECTION ALGORITHM FOR SYSTEM WITH 12V

## TIMING WAVEFORM FOR SECTOR PROTECTION FOR SYSTEM WITHOUT 12V

TIMING WAVEFORM FOR CHIP UNPROTECTION FOR SYSTEM WITHOUT 12V

## SECTOR PROTECTION ALGORITHM FOR SYSTEM WITHOUT 12V

## **CHIP UNPROTECTION ALGORITHM FOR SYSTEM WITHOUT 12V**

## ID CODE READ TIMING WAVEFORM MODE

## **ORDERING INFORMATION**

## PLASTIC PACKAGE

| PART NO.       | ACCESS TIME | OPERATING CURRENT | STANDBY CURRENT | PACKAGE       |

|----------------|-------------|-------------------|-----------------|---------------|

|                | (ns)        | MAX.(mA)          | MAX.(uA)        |               |

| MX29F002TPC-70 | 70          | 30                | 1               | 32 Pin PDIP   |

| MX29F002TPC-90 | 90          | 30                | 1               | 32 Pin PDIP   |

| MX29F002TPC-12 | 120         | 30                | 1               | 32 Pin PDIP   |

| MX29F002TTC-70 | 70          | 30                | 1               | 32 Pin TSOP   |

|                |             |                   |                 | (Normal Type) |

| MX29F002TTC-90 | 90          | 30                | 1               | 32 Pin TSOP   |

|                |             |                   |                 | (Normal Type) |

| MX29F002TTC-12 | 120         | 30                | 1               | 32 Pin TSOP   |

|                |             |                   |                 | (Normal Type) |

| MX29F002TQC-70 | 70          | 30                | 1               | 32 Pin PLCC   |

| MX29F002TQC-90 | 90          | 30                | 1               | 32 Pin PLCC   |

| MX29F002TQC-12 | 120         | 30                | 1               | 32 Pin PLCC   |

| MX29F002BPC-70 | 70          | 30                | 1               | 32 Pin PDIP   |

| MX29F002BPC-90 | 90          | 30                | 1               | 32 Pin PDIP   |

| MX29F002BPC-12 | 120         | 30                | 1               | 32 Pin PDIP   |

| MX29F002BTC-70 | 70          | 30                | 1               | 32 Pin TSOP   |

|                |             |                   |                 | (Normal Type) |

| MX29F002BTC-90 | 90          | 30                | 1               | 32 Pin TSOP   |

|                |             |                   |                 | (Normal Type) |

| MX29F002BTC-12 | 120         | 30                | 1               | 32 Pin TSOP   |

|                |             |                   |                 | (Normal Type) |

| MX29F002BQC-70 | 70          | 30                | 1               | 32 Pin PLCC   |

| MX29F002BQC-90 | 90          | 30                | 1               | 32 Pin PLCC   |

| MX29F002BQC-12 | 120         | 30                | 1               | 32 Pin PLCC   |

## **ORDERING INFORMATION**

## PLASTIC PACKAGE

| PART NO.        | ACCESS TIME | OPERATING CURRENT | STANDBY CURRENT | PACKAGE       |

|-----------------|-------------|-------------------|-----------------|---------------|

|                 | (ns)        | MAX.(mA)          | MAX.(uA)        |               |

| MX29F002NPC-70  | 70          | 30                | 1               | 32 Pin PDIP   |

| MX29F002NPC-90  | 90          | 30                | 1               | 32 Pin PDIP   |

| MX29F002NPC-12  | 120         | 30                | 1               | 32 Pin PDIP   |

| MX29F002NTTC-70 | 70          | 30                | 1               | 32 Pin TSOP   |

|                 |             |                   |                 | (Normal Type) |

| MX29F002NTTC-90 | 90          | 30                | 1               | 32 Pin TSOP   |

|                 |             |                   |                 | (Normal Type) |

| MX29F002NTTC-12 | 120         | 30                | 1               | 32 Pin TSOP   |

|                 |             |                   |                 | (Normal Type) |

| MX29F002NTQC-70 | 70          | 30                | 1               | 32 Pin PLCC   |

| MX29F002NTQC-90 | 90          | 30                | 1               | 32 Pin PLCC   |

| MX29F002NTQC-12 | 120         | 30                | 1               | 32 Pin PLCC   |

| MX29F002NBPC-70 | 70          | 30                | 1               | 32 Pin PDIP   |

| MX29F002NBPC-90 | 90          | 30                | 1               | 32 Pin PDIP   |

| MX29F002NBPC-12 | 120         | 30                | 1               | 32 Pin PDIP   |

| MX29F002NBTC-70 | 70          | 30                | 1               | 32 Pin TSOP   |

|                 |             |                   |                 | (Normal Type) |

| MX29F002NBTC-90 | 90          | 30                | 1               | 32 Pin TSOP   |

|                 |             |                   |                 | (Normal Type) |

| MX29F002NBTC-12 | 120         | 30                | 1               | 32 Pin TSOP   |

|                 |             |                   |                 | (Normal Type) |

| MX29F002NBQC-70 | 70          | 30                | 1               | 32 Pin PLCC   |

| MX29F002NBQC-90 | 90          | 30                | 1               | 32 Pin PLCC   |

| MX29F002NBQC-12 | 120         | 30                | 1               | 32 Pin PLCC   |

## MX29F002/002N

## PACKAGE INFORMATION

#### **32-PIN PLASTIC DIP**

| ITEM | MILLIMETERS | INCHES      |

|------|-------------|-------------|

| А    | 42.13 max.  | 1.660 max   |

| В    | 1.90 [REF]  | .075 [REF]  |

| С    | 2.54 [TP]   | .100 [TP]   |

| D    | .46 [Typ.]  | .050 [Typ.] |

| E    | 38.07       | 1.500       |

| F    | 1.27 [Typ.] | .050 [Typ.] |

| G    | 3.30 ± .25  | .130 ± .010 |

| Н    | .51 [REF]   | .020 [REF   |

| I    | 3.94 ± .25  | 1.55 ± .010 |

| J    | 5.33 max.   | .210 max.   |

| К    | 15.22 ± .25 | .600 ± .10  |

| L    | 13.97 ± .25 | .550 ± .010 |

| М    | .25 [Typ.]  | .010 [Typ.] |

NOTE: Each lead certerline is located within .25mm[.01 inch] of its true position [TP] at a maximum at maximum material condition.

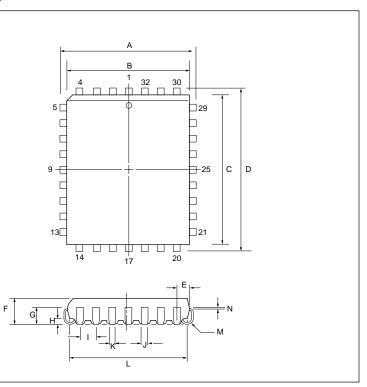

## 32-PIN PLASTIC LEADED CHIP CARRIER (PLCC)

| ITEM | MILLIMETERS     | INCHES      |

|------|-----------------|-------------|

| А    | 12.44 ± .13     | .490 ± .005 |

| В    | 11.50 ± .13     | .453 ± .005 |

| С    | $14.04 \pm .13$ | .553 ± .005 |

| D    | 14.98 ± .13     | .590 ± .005 |

| E    | 1.93            | .076        |

| F    | 3.30 ± .25      | .130 ± .010 |

| G    | 2.03 ± .13      | .080 ± .005 |

| Н    | .51 ± .13       | .020 ± .005 |

| I    | 1.27 [Typ.]     | .050 [Typ.] |

| J    | .71 [REF]       | .028 [REF]  |

| к    | .46 [REF]       | .018 [REF]  |

| L    | 10.40/12.94     | .410/.510   |

|      | (W) (L)         | (W) (L)     |

| М    | .89R            | .035R       |

| Ν    | .25[Typ.]       | .010[Typ.]  |

NOTE: Each lead certerline is located within .25mm[.01 inch] of its true position [TP] at a maximum at maximum material condition.

## MX29F002/002N

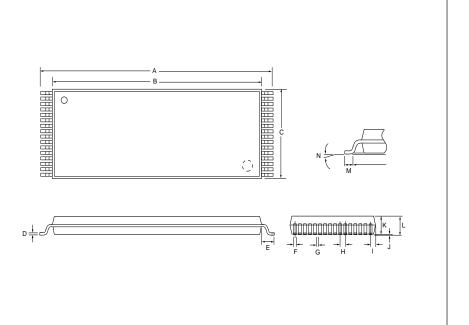

#### **32-PIN PLASTIC TSOP**

| ITEM | MILLIMETERS | INCHES      |

|------|-------------|-------------|

| А    | 20.0 ± .20  | .078 ± .006 |

| В    | 18.40 ± .10 | .724 ± .004 |

| С    | 8.20 max.   | .323 max.   |

| D    | 0.15 [Typ.] | .006 [Typ.] |

| Е    | .80 [Typ.]  | .031 [Typ.] |

| F    | .20 ± .10   | .008 ± .004 |

| G    | .30 ± .10   | .012 ± .004 |

| Н    | .50 [Typ.]  | .020 [Typ.] |

| I    | .45 max.    | .018 max.   |

| J    | 0 ~ .20     | 0 ~ .008    |

| к    | 1.00 ± .10  | .039 ± .004 |

| L    | 1.27 max.   | .050 max.   |

| М    | .50         | .020        |

| Ν    | 0~5°        | .500        |

NOTE: Each lead certerline is located within .25mm[.01 inch] of its true position [TP] at a maximum at maximum material condition.

## **REVISION HISTORY**

| Revision | Description                                                                               | Page              | Date        |

|----------|-------------------------------------------------------------------------------------------|-------------------|-------------|

| 0.2      | Device codes are revised to 00B0h/0034h compatible with AMD's                             |                   | JUN/29/1998 |

| 0.3      | The feature of sector unprotect is revised to chip unprotect                              |                   | JUL/07/1998 |

| 0.4      | Device ID codes are revised to B0h/34h compatible with AMD's                              |                   | JUL/29/1998 |

| 0.5      | Sector Protect Verification is added on the software command table                        |                   | AUG/18/1998 |

| 0.6      | Modify the block diagram                                                                  |                   | AUG/28/1998 |

| 0.7      | Modify the Q3 Status into "0" for Exceeded Time Limits in Write<br>Operation Status table | P8                | SEP/10/1998 |

| 0.8      | Change IOH value at DC CHARACTERISTICS                                                    | P14               | NOV/10/1998 |

|          | Change resistance value at SWITCHING TEST CIRCUITS                                        | P17               |             |

| 0.9      | To correct typing error                                                                   | P8,23,28<br>31,32 | DEC/09/1998 |

## MACRONIX INTERNATIONAL CO., LTD.

HEADQUARTERS: TEL:+886-3-578-8888 FAX:+886-3-578-8887

EUROPE OFFICE: TEL:+32-2-456-8020 FAX:+32-2-456-8021

JAPAN OFFICE: TEL:+81-44-246-9100 FAX:+81-44-246-9105

SINGAPORE OFFICE: TEL:+65-747-2309 FAX:+65-748-4090

TAIPEI OFFICE: TEL:+886-3-509-3300 FAX:+886-3-509-2200

MACRONIX AMERICA, INC. TEL:+1-408-453-8088 FAX:+1-408-453-8488

CHICAGO OFFICE: TEL:+1-847-963-1900 FAX:+1-847-963-1909

http://www.macronix.com